| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

- 가상화

- 파이썬

- 신경회로망

- Neural Network

- 갤럭시탭S8울트라

- SSM

- 고려대학교

- Friendship

- 멤버십

- 신경망

- Bidirectional Associative Memory

- 패턴인식

- 동아리

- 빅데이터

- 패턴 인식

- 증강현실

- 하이퍼바이저

- Python

- 물걸레로봇청소기추천

- Google App Engine

- 삼성전자 소프트웨어멤버십 SSM

- hopfield network

- BAM

- 구글 앱 엔진

- 삼성

- 물걸레자동세척로봇청소기

- NarwalFreo

- 인공지능

- 나르왈프레오

- 삼성소프트웨어멤버십

- Today

- Total

정보공간_1

[3기 전주 전환규] Place & Route Part.2 본문

안녕하세요. 전주멤버십 22기 전환규 입니다.

어느덧 화창한 봄 날씨가 되었네요.

지난달에 이어서 Place & Route Part.2를 연재할 생각합니다.

4. Design & Timing Setup

- Netlist In - Verilog To CEL ... [Click]

[그림 8] Create CELL

# Verilog To CEL

[그림 9] Verilog To Cell

a. Library Name : JHK (임의로 설정하시면 됨)

b. Verilog File Name : CBJHK_layout.v

(PAD Netlist File or Memory 사용시에는 공정사의 DRC Tool에 의해 정리된 파일)

c. Output Cell Name : CBJHK_PAD

(PAD Netlist File의 Top Module Name 으로 적어 주는게 좋다. 생성할 Cell Name 이다.)

d. Top Module Name : Pad Netlist File의 Top Module Name

e. Tech File Name : std150e_prim_6m.techgen.tf (Astro Library/TECH 폴더 안에 있다.)

f. Reference Library [Click]

# Reference Library

[그림 10] Reference Library

a. Browse... [Click]

b. Library Add

1) Standard Cell Library (공정사에서 제공하는 Library - 회사마다 다름)

std150e_60poi_io_6lm_071011 [Add]

std150e_60poi_power_6lm_070420 [Add]

std150e_prim_050504 [Add]

2) Macro Library

spsram_hd_256x32m4 [Add]

- Macro Cell Library는 Create Memory Library 단계에서 생성한 Library 이다.

c. Hide [Click]

d. Global Net Options [Click]

# Global Net Options

[그림 11] Global Net Options

a. Net Name : VDD

b. Port pattern : VDD.*

c. Apply [Click]

d. Net Name : VSS

e. Port Pattern : VSS.*

f. Apply [Click]

g. Hide [Click]

h. Verilog To Cell Window OK [Click]

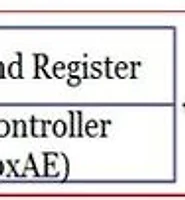

# Library - Show Refs ... [Click]

[그림 12] Show Ref Libraries

a. Library Name : KD

(자신이 생성한 Library Name)

b. OK [Click]

# Open Library & Cell

[그림 13] Open Library & Cell

a. Library - Open ... [Click]

b. Library Name : KD

(자신이 생성한 Library Name)

c. OK [Click]

d. Cell - Open ... [Click]

e. Cell Name : CBJHK_PAD

(Verilog To Cell 에서 작성한 Output Cell Name)

f. OK [Click]

[그림 14] Open Cell

# Mark Module Instances Preserved

[그림 15] Hierarchy Preservation

a. Cell - Mark Module Instances Preserved ... [Click]

b. Flattened Cell Name (.EXP .CEL) : CBJHK_PAD

(Verilog To Cell에서 작성한 Output Cell Name)

c. OK [Click]

이번 과정을 통해 Design & Timing Setup 과정 중 Design Setup 과정을 마쳤습니다. 이후에 Load SDC 를 통해 sdc 파일을 읽어 Timing Setup 과정을 할 것입니다. Floorplanning 과정을 통해서 전체적인 칩의 사이즈를 결정할 것이며 칩의 모양을 간단하게 살펴 볼 수 있습니다.

이상 마치겠습니다. 다음달에는 좀 더 알찬 내용으로 돌아오겠습니다.

'IT 놀이터 > Elite Member Tech & Talk' 카테고리의 다른 글

| [3기 강남 정준호] Console & Shell 개발 (0) | 2013.05.06 |

|---|---|

| [3기 강남 백정의] Flash에서 현재 화면을 서버에 저장 및 불러오기 (0) | 2013.05.06 |

| [3기 강남 백정의] 플래시의 비트맵을 활용한 영상을 재생시키고 레이어 추가 (0) | 2013.04.06 |

| [3기 강남 정준호] KeyBoard & Monitor Device Driver (0) | 2013.04.05 |

| [3기 강남 정준호] Work-Queue Working Flow (0) | 2013.04.05 |