| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

- BAM

- 신경망

- 구글 앱 엔진

- 물걸레자동세척로봇청소기

- 삼성전자 소프트웨어멤버십 SSM

- Google App Engine

- SSM

- 삼성소프트웨어멤버십

- Bidirectional Associative Memory

- 갤럭시탭S8울트라

- 파이썬

- 증강현실

- 하이퍼바이저

- 나르왈프레오

- Friendship

- Neural Network

- 멤버십

- Python

- 신경회로망

- 물걸레로봇청소기추천

- 가상화

- 패턴 인식

- 빅데이터

- 고려대학교

- 동아리

- hopfield network

- 인공지능

- NarwalFreo

- 패턴인식

- 삼성

- Today

- Total

정보공간_1

[3기 전주 전환규] Place & Route Part.3 본문

안녕하세요. 전주멤버십 22기 전환규 회원입니다.

지난달에 이어서 Place & Route Part.3를 연재하도록 하겠습니다.

제가 1월부터 연재중인 내용들은 모두 Digital Chip 설계 입니다.

이전부터 보시면 Macro Block 라이브러리를 설정하고 Macro Block을 가져오는데 이 부분에 Macro Block을

아날로그로 설계한 파트를 가져오시면 자신이 설계한 칩이 Mixed(Analog+Digital)이 됩니다.

4. Disign & Timing Setup

[그림 1. Open Cell]

그림 1은 패드 정보를 불러온 모습입니다. spsram_hd_256x32m4.FRAM 옆에 보시면 자신이 설계한 게이트들의 모습이 뭉쳐 있는 것을 확인 할 수 있습니다.

[그림 2. Hierarchy Preservation]

# Mark Module Instances Preserved

a. Cell - Mark Module Instances Preserved ... [Click]

b. Flattened Cell Name (.EXP .CEL) : CBJHK_PAD (Verilog To Cell 에서 작성한 Output Cell Name)

c. OK [Click]

5. Convert ITF to TLU+

[그림 3. Convert ITF to TLU+]

# Convert ITF to TLU+

a. Tech File - ITF to TLU+ [Click]

b. Library Name : KD (자신이 생성한 Library Name)

c.

Min RCTable File : L13_CELL_BST_6LM_DUMMY

Nom RCTable File : L13_CELL_TYP_6LM_DUMMY

Max RCTable File : L13_CELL_WST_6LM_DUMMY

Star-RCXT RCTable File : L13_CELL_6LM.map

d. Sanity Check [Click]

e. OK [Click]

# TLU+ & MAP

a. TLU+.tar File

설정을 완료 하면 위의 그림 처럼 모두 [ Passed! ] 가 된다.

6. Load SDC

[그림 4. Load SDC]

# Load SDC

# Tools - Astro [Click]

a. Timing - Load sdc [Click]

b. SDC File Name : CBJHK_sdc.sdc (Design Compiler에서 생성한 sdc 파일을 로드한다.)

c. OK [Click]

sdc 파일을 불러오기하면 위의 그림 처럼 Load SDC succeeded 가 표시된다. Clock tree synthesis를 위해서는 sdc 파일이 필요하다.

7. Timing Setup

[그림 5. Timing Setup]

# AstroTime (tm) Timing Setup

a. Timing - Timing Setup ... [Click]

b. Parasitics [Click]

c. Parasitic Source : LPE

d. LPE Mode : Auto

e. Operating Cond : Max, Min

f. Capacitance Model : TLU+

g. Apply [Click]

8. Floorplanning

[그림 6. Load TDF]

# Load TDF

a. Design Setup - Load TDF ... [Click]

b. Cell Name : CBJHK_PAD

c. TDF File Name : PadFileName.tdf

d. OK [Click]

[그림 7. Floor Planner]

# Floor Planner

a. Design Setup - Set Up Floorplan ... [Click]

b. Horizontal Row / Double Back / Start First Row / Flip First Row [Check]

c. Row/Core Ratio : 1

Core Utilization : 0.7

d. Set [Click]

e. Core To Left & Core To Right : (4000 - ((137.62 * 2) + Core Width)) / 2

f. Core To Bottom & Core To Top : (4000 - ((137.62 * 2) + Core Height)) / 2

g. OK [Click]

# IO pad : 137.62

PDF 파일에서 IO pad의 사이즈를 읽고 코어의 전체 사이즈를 바탕으로 계산해서 값을 넣어주면 된다.

[그림 8. Cell]

그림 8은 Floor Planner로 설정한 뒤의 모습이다. 셀을 확대해서 좌측 아래 부분의 좌표를 보면 (0, 0) 이며,

우측 아래를 확대해 보면 (4000, 0)이 나올 것입니다.. 정확하게 확인하기 위해서는 각 끝의 좌표들을 확인해 보는 것이 좋습니다. (4000, 4000) 부분이 정확하게 맞아들어가면 제대로 설정한 것입니다. [4000 이라는 숫자는 본인이 MPW과정에서 사용한 칩의 사이즈가 4x4여서 4000 인 것이다.]

만약 위 과정이 틀리면 Floor Planner 부분에서 정확한 계산을 다시 해야한다.

지금까지 Chip 설계 과정중에 Place & Route과정에서 Floorplanning까지 살펴 보았습니다. 이후 Pad Filter 등 VDD, VSS 등 많은 과정들이 남아 있습니다. 혹시나 궁금한 분들은 flowerfou@gmail.com 으로 메일을 보내주시면 자세하게 알려드리겠습니다.

'IT 놀이터 > Elite Member Tech & Talk' 카테고리의 다른 글

| [4기 강남 이상훈] Mobile Accessibility[모바일 애플리케이션 접근성 지침]-Part 2 (0) | 2013.10.20 |

|---|---|

| [4기 강남 이상훈] Mobile Accessibility[모바일 접근성]-Part 1 (0) | 2013.10.02 |

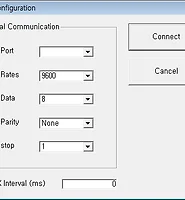

| [3기 신촌 최기환] WPF 활용 - 시리얼 통신 (0) | 2013.05.10 |

| [3기 대전 김재원] Linux Kernel - Data Structure (2) (0) | 2013.05.09 |

| [3기 강북 김승현] ffmpeg 를 이용한 간단한 동영상 플레이어 제작 #3 (1) | 2013.05.06 |